- 您现在的位置:买卖IC网 > Sheet目录1996 > ICS181M-53T (IDT, Integrated Device Technology Inc)IC CLOCK GEN LOW EMI 8-SOIC

DATASHEET

LOW EMI CLOCK GENERATOR

ICS181-53

IDT / ICS LOW EMI CLOCK GENERATOR

1

ICS181-53

REV C 051310

Description

The ICS181-53 generates a low EMI output clock from

a clock or crystal input. The device uses IDT’s

proprietary mix of analog and digital Phase Locked

Loop (PLL) technology to spread the frequency

spectrum of the output, thereby reducing the frequency

amplitude peaks by several dB.

The ICS181-53 offers center spread selection of

+/-0.625% and +/-1.875%. Refer to the MK1714-01/02

for the widest selection of input frequencies and

multipliers.

IDT offers a complete line of EMI reducing clock

generators. Consult us when you need to remove

crystals and oscillators from your board.

Features

Pin and function compatible to Cypress W181-53

Packaged in 8-pin SOIC

Provides a spread spectrum output clock

Accepts a clock input and provides same frequency

dithered output

Input frequency of 46 to 75 MHz for Clock input

Peak reduction by 7dB - 14dB typical on 3rd - 19th

odd harmonics

Spread percentage selection for +/-0.625% and

+/-1.875%

Operating voltage of 3.3 V and 5 V

Advanced, low-power CMOS process

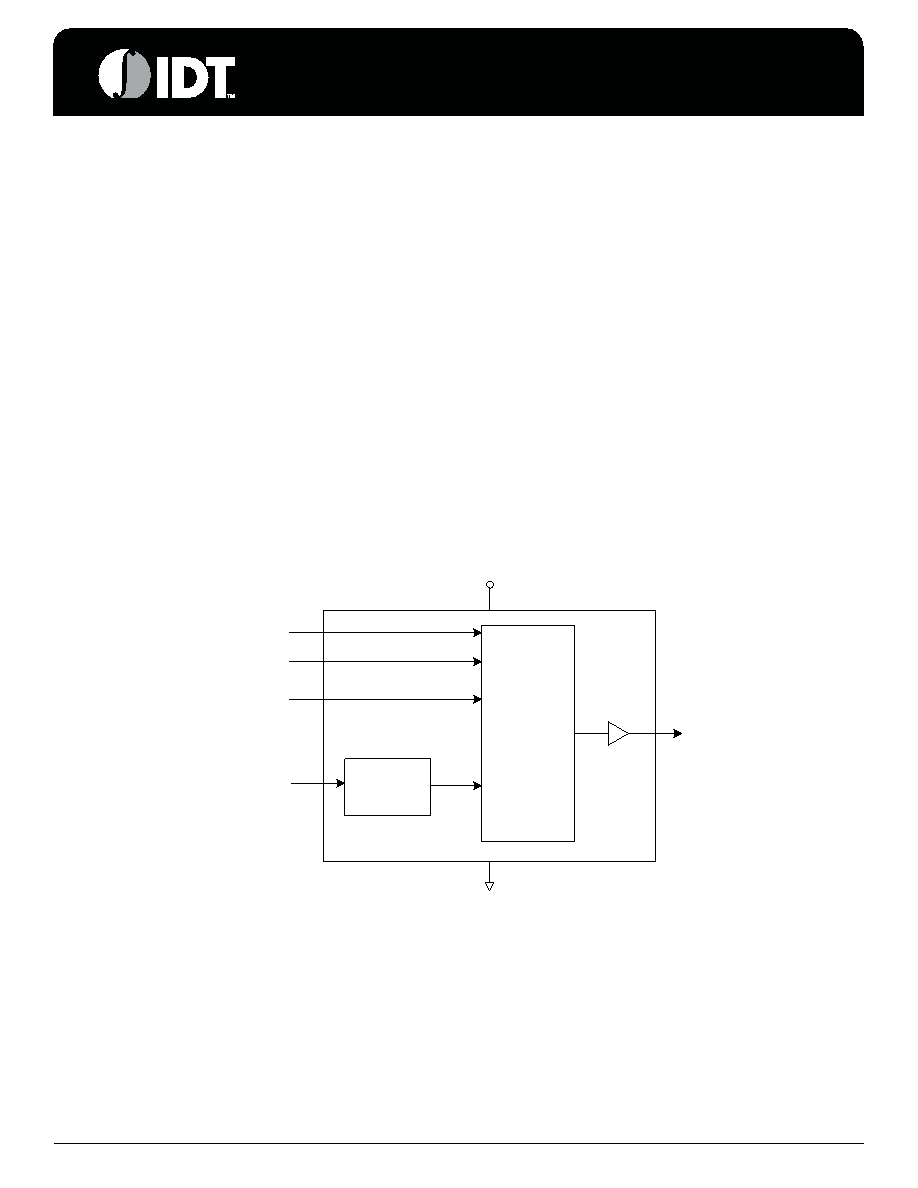

Block Diagram

PLL Clock

Synthesis

and Spread

Spectrum

Circuitry

SS%

CLK

GND

VDD

SSON#

CLKIN

Clock Buffer

FS1

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ICS181MI-01LF

IC CLOCK GEN LOW EMI 8-SOIC

ICS2402MLFT

IC MULTIPLIER/ZD BUFFER 8-SOIC

ICS270PGILF

VCXO CLK TRPL PLL PROGR 20-TSSOP

ICS281PGILF

IC CLK SYNTH TRPL PLL 16-TSSOP

ICS411MLF

IC PC PERIPHERAL CLOCK 8-SOIC

ICS477R-05T

IC QUAD PLL VCXO FOR HDTV 28QSOP

ICS487G-25T

IC QUAD PLL FOR DTV 16-TSSOP

ICS501AMILF

IC PLL CLK MULTIPLIER 8-SOIC

相关代理商/技术参数

ICS181MI-01

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

ICS181MI-01LF

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

ICS181MI-01LFT

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

ICS181MI-01T

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

ICS181MI-02

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG

ICS181MI-02LF

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

ICS181MI-02LFT

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR)

ICS181MI-02T

功能描述:IC CLOCK GEN LOW EMI 8-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG